w10. 가상 메모리의 기초 1

- vitual M의 개요

- paging

- segmentation

- segmentation-paging 혼용기법

Virtual Memory System

virtual 메모리

각 process에 자신만의 가상 메모리공간 제공(HHD에 존재). / 주소 0번지부터 시작.

0번지부터 시작한다는 것만 알면 되기 때문에, 프로그래머들은 메모리에 올라갈 주소공간을 고려하지 않아도 된다는 장점이 있음.

virtual memory 구성

virtual M영역: cpu가 바라보는 메모리 영역

+

physical M영역: 실제 물리적인 메모리 영역 / MMU의 관리 O

+

swap 영역: 물리적 메모리에서 벗어난(쫓겨난) 프로세스 모아두는 영역 / MMU의 관리 O

==> MMU가 사용할 수 있는 메모리의 전체 크기

🚶♀️ 불연속 메모리 할당 - paging 기법의 구현

/ internal 발생가능, external은 X

paging: 고정분할 방식을 이용한 Virtual M 관리기법

#frame

물리메모리 주소공간을 고정된 같은 크기로 나눠 사용

physical M의 분할된 각 영역을 번호 매겨 관리.

#page

가상메모리 주소공간을 고정된 같은 크기로 나눠 사용.

virtual M의 분할된 각 영역을 번호 매겨 관리.

* page와 frame의 크기는 동일. > page는 어디에나 배치될 수 있음.

#page table

어떤 페이지가 어떤 프레임에 있는지에 대한 매핑 정보 저장

프로세스마다 하나씩 존재.(physical M안에 존재)

CPU가 physical M의 특정 주소로 접근하는 방법

1. logical 주소에(in virtual M) 나와있는 page 번호를 확인

2. page table로 이동 후, 해당 page 번호에 따른 frame 번호를 확인 .

3. 해당 frame 번호를 가진 physical M의 주소로 이동.

🏃♂️ paging 시스템의 하드웨어 구조

* d만큼 떨어진 부분은 page에서나 frame에서나 동일하게 적용됨.

1. cpu는 virtualM의 페이지 4에서 d만큼 떨어진 부분을 접근하길 원함.

2. MMU로 이동해 logical 주소를 physical 주소로 변환.

3. 변환된 physical 주소를 바탕으로 physical M의 1번 frame으로 접근.

4. 1번 frame에서 d만큼 떨어져 있는 주소를 CPU에게 전달.

🚴♀️ paging 기법의 주소 변환

가상주소 VA=<P,D>

VA: 가상주소

P: 페이지

D: 거리(=offset, 페이지의 처음위치에서 해당 주소까지의 거리)

물리주소 PA=<F,D>

PA: 물리주소(실제주소)

F: 프레임

D: 거리(=offset, 프레임의 처음위치에서 해당 주소까지의 거리)

page table 이용해서 P->F (D는 그대로)

*D는 page와 frame의 크기를 동일하게 나눠서 변경하지 않음.

Ex)

1. 한 페이지의 크기가 10byte인 virtualM에서 가상주소 24번지(접근하려는 주소)

*가상주소/ 페이지크기 => 몫: P, 나머지:D

24/10=> P: 2, D: 4

VA=<2,4>

2. 한 페이지의 크기가 10byte인 가상주소 30번지

30/10=> P:3, D:0

VA=<3,0>

3. 한 페이지의 크기가 2의 10승(1024)인 가상주소 980번지

980/1024=> P:0, D:980

VA=<0,980>

〰️

<MEMORY 주소>

4Gbyte인 메모리를 4Kbyte크기로 나누면 몇개의 block?

4G= 2의 32승

4K= 2의 12승

=> 나누면 2의 20승개의 block 생김.

〰️

<16bit 컴퓨터에서의 예제>

- p: 6bit

- d: 10bit

16bit CPU의 컴퓨터에서, 한 page의 크기가 2의 10승 byte일때

* 2의 16승/ 2의 10승 = 2의 6승

=> 전체 page수는 2의 6승(64)개

3. 한 페이지의 크기가 2의 10승(1024)인 가상주소 980번지 - 다시 ( in 16 bit com)

980/1024=> P:0, D:980

VA=<0,980>

980= 0000 0011 1101 0100(2) - 16bit

p(6bit): 000000

d(10bit): 1111010100 (980)

🚶 page table 관리 (in physical M)

각 page table의 시작주소: Page Table Base Register (PTBR, page table 기준레지스터)

각 page table의 크기.길이주소: Page Table Length Register(PTLR, 끝 위치 저장됨)

Physical M의 크기가 작을 때는 프로세스만 swap area로 옮겨지는 것 아니라, page table의 일부도 옮겨짐.

🚶♀️ page table의 mapping방식

1. direct mapping(직접매핑)

page table 전체가 Physical M의 운영체제 영역에 존재. 부가작업 없이 바로 주소변환 가능

2. associative mapping(연관매핑)

- 동적주소할당의 성능향상을 시키는 방법. 일반적으로 TLB(cache M) 사용

- 일부 내용만 무작위로 accociative M으로 가져오는데, 무작위라서 page번호와 frame번호 둘 다 표시.

- 주소변환 방법

1. associative M(TLB) 내의 page table 모두 검색

2. 원하는 frame 번호를 얻지 못하면 main M에 있는 전체 page table 검색.

=> 검색 실패 시 main M에서 다시 검색해서 시간낭비임

- TLB: translation look-ahead buffer, 주소 변환을 위한 캐쉬 메모리. -MMU 내

TLB hit: cpu가 TLB에 주소 갖는지 요청하고, 있다면 TLB에서 cpu로 주소 전달 후 메모리의 해당주소로 이동함. => 매우 빠름

TLB miss: 원하는 page번호가 없다면, main M에 저장된 direct mapping table(page table) 사용해 frame 번호로 변환

TLB 단점: miss가 빈번할 경우 시스템 성능의 저하가 발생.

랜덤으로 페이지 테이블의 일부를 가짐=> 검색시간 필요.

모든 TLB를 검색한 후에야 원하는 page가 TLB에 없다는 것을 알 수 O

- parallel searching(병렬탐색) 방법의 TLB를 연관 레지스터라고도 함.

* parallel searching 효과

1. TLB searching 시간 감소

2. TLB miss일 땐 TLB를 모두 찾는 시간을 줄일 수 O

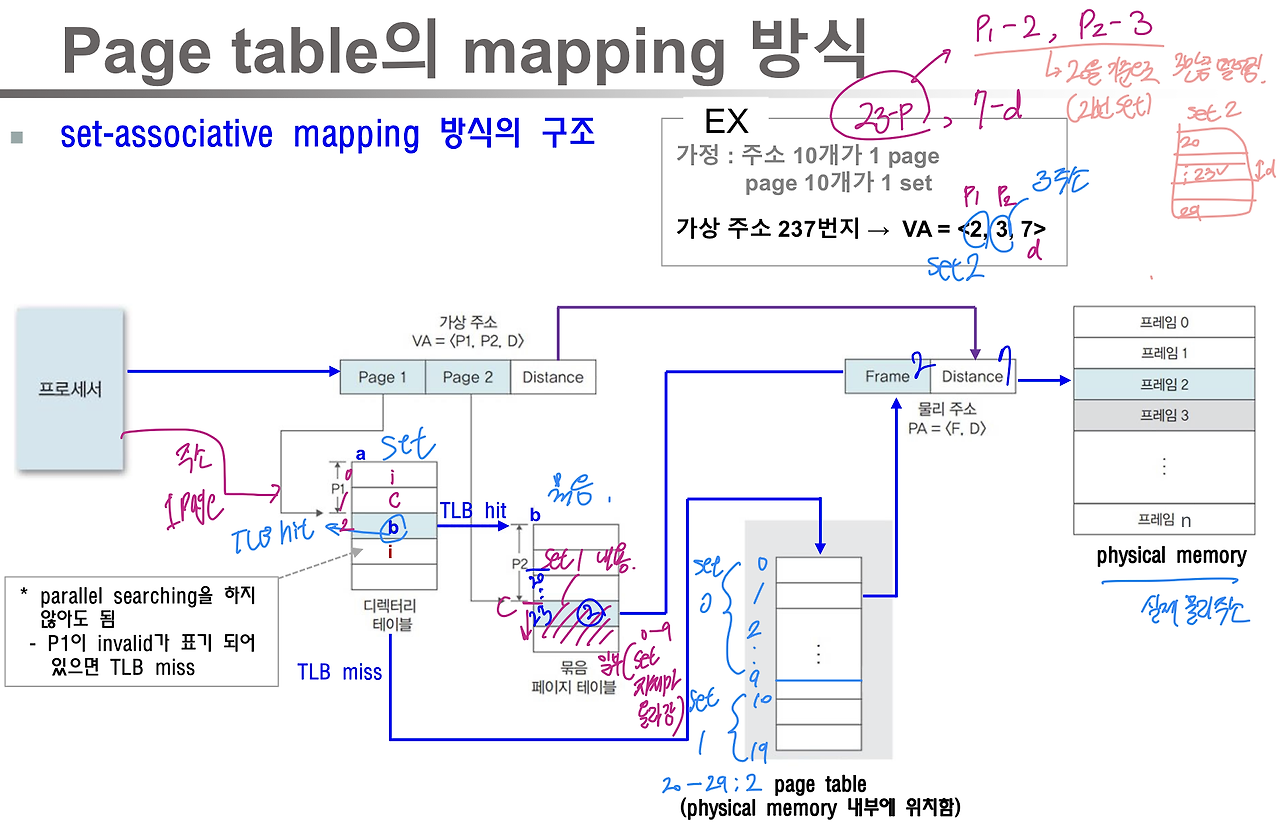

3. set-associative mapping(집합-연관매핑)

page table을 같은 크기로 여러묶음으로 나누고,

set(directory table)을 새로 만들어 각 묶음의 시작주소를 넣어둠. - 해당 묶음이 현재 TLB에 있는지, main M에 있는지 알 수 O

디렉토리 테이블(set)을 살펴보면 원하는 table 묶음의 위치를 알 수 있기에, 전체 table 보지 않아도 TLB miss를 바로 알 수 있음.

🏃 Set-associative mapping과 associative mapping 비교

associative mapping

Physical M의 데이터가 무작위로 associative M(TLB)로 올라옴.

=> 원하는 frame 번호 얻기 위해 모든 page table 검색해야 하는 문제 존재.

set - associative mapping

(=directory mapping. SET과 TLB로 나눔)

- page table을 일정한 set으로 자르고, 자른 집합의 단위로 physical M에 가져옴

- page table을 n개씩 자르고 관리하는 page table을 하나 더 생성.

- 새로 생성한 set table 내용

일정하게 자른 page table의 위치정보(TLB/ Physical M) 표시

=> set table을 통해 원하는 page table entry의 위치 정보를 쉽게 파악 가능~!

🏃➡️ Set-associative mapping의 가상주소

형태: VA=<P1(set), P2(set안의 위치정보-묶음), D>

page table이 일정 크기의 묶음으로 나뉘어서 세개의 요소 필요.

프로세스가 특정 주소를 요구 => VA=<P1,P2,D>로 변환 => P1을 이용해 directory table(set table)에서 주소 찾음

i(invalid) - TLB miss

원하는 table이 physical M에 있다면 묶음 table의 시작 주소가 명시되어 있음.

'OS' 카테고리의 다른 글

| 벼락치기 - 운영체제 12 (2) | 2024.06.10 |

|---|---|

| 벼락치기 - 운영체제 11 (2) | 2024.06.09 |

| 벼락치기 - 운영체제 9 (2) | 2024.06.09 |